# Low power 1 bit-cmos Full adder based on Reduction of parasitic capacitance through Layout optimization

Dayadi. Lakshmaiah<sup>1</sup>

Dr.M.V.Subramanyam<sup>2</sup>

Dr.K.Satya Prasad<sup>3</sup>

<sup>1</sup>Ph.D Research scholar ECE Department, JNTU, Kakinada, Asso.pro ,NIET ,HYD India. laxmanrecw@gmail.com

<sup>2</sup>Principal and Professor of ECE Department, Santhi Ram Engineering College, Nandyala, India. mvsraj@yahoo.com

<sup>3</sup>Professor of ECE Department and Rector, JNTU Kakinada, Kakinada, India. prasad\_kodati@yahoo.co.in

### Abstract:-

The Aim of this paper is to calculate the MOSFET parasitic capacitances, and then based on the results obtained we can further see the impact of MOSFET physical parameters on these parasitic capacitances. These capacitances have a direct impact in the speed of operation of MOSFET circuits. Therefore, in order to increase the speed of operation, it is necessary that the parasitic capacitances are reduced to a minimum possible level that the technological process allows. We have analyzed the different types of capacitance effect as a function of the MOSFET dimensions. Operating an Integrated circuit at the prescribed Reduction of parasitic capacitance through Layout optimization is preferable for reliable circuit operation. In this work we proposed to design 1 –bit full adder by "Reduction of parasitic capacitance through Layout optimization" we measured pars tic capacitance, power consumption, leakage current, layout area, Delay ,etc parameters. The results are compared with the previous work and shown that Power is saved 63%, 55% of leakage current , 72% of total capacitance at input A, 63% of total capacitance at input B, 74% of total capacitance at input C, 86% of total capacitance at sum, , 86% total capacitance at carry, 88% of gate capacitance,77% of diffusion capacitance ,86% of metal capacitance and 100% of crosstalk capacitance and 99% of delay and 71% of Area. We have performed simulations using 90 Nanometer (nm) Micro wind 3 CMOS layout CAD Tool for design.

Key words: layout optimization, total capacitance, diffusion capacitance, gate capacitance, metal capacitance, crosstalk capacitance, leakage current (Ion+Ioff), Area, Delay

1. Introduction:-

Power dissipation has become a prime constraint in high performance applications, especially in portable and battery operated ASIC systems so it is necessary to reduce power consumption. Power consumption is proportional to square of supply voltage [1] cmos circuits the cost of lower supply voltage is lower performance. Scaling the threshold voltage can limit this performance loss to some extent but results in increased leakages [2] The advantage of GDI technique two-transistor implementation of complex logic functions and in-cell swing restoration under certain operating conditions, are unique within existing lowpower design techniques.[3] Power gating is one such well known technique where a sleep transistor is added between actual ground rail and circuit ground (called virtual ground) [4], this device is turned off in the sleep mode to cut-off the leakage path. It has been shown that this technique provides a substantial reduction in leakage at a minimal impact on performance [5], [6], [7], [8]. With the scaling of transistor dimensions extrinsic, or lay- out dependent, parasitic capacitance contributions, such as poly-to-contact coupling, as well as corner c a p a c i t a n c e , become more and more important with respect to intrinsic contributions [10]. Accumulated systematic numerical data that clarify the dependence of the capacitance on gate length  $L_G$ , gate electrode thickness  $t_p$ , and gate oxide thickness  $t_{ox}[11]$ .

## 2. Proposed work:-

### 2.1. Parasitic capacitance:-

Any two conductors separated by insulator have capacitance; gate to channel capacitor is very important Logic-cell delay results from transistor resistance, transistor (intrinsic) parasitic capacitance, and load (extrinsic) capacitance. When one logic cell drives another, the parasitic input capacitance of the driven cell becomes the load capacitance of the driving cell and this will determine the delay of the driving cell. An unwanted coupling from a neighboring signal wire to a N/W node introduces an interference that is generally called cross talk. Cross talk making wire delay more, more unpredictable.

In electrical circuits, parasitic capacitance, stray capacitance or, when relevant, self-capacitance (of an inductor), is an unavoidable and usually unwanted capacitance that exists between the parts of an electronic component or circuit simply because of their proximity to each other. All actual circuit elements such as inductors, diodes, and transistors have internal capacitance, which can cause their behavior to depart from that of 'ideal' circuit elements. In addition, there is always non-zero capacitance between any two conductors; this can be significant at higher frequencies with closely spaced conductors, such as wires or printed circuit board traces.

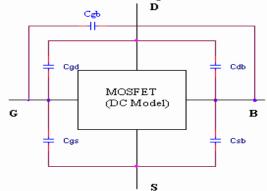

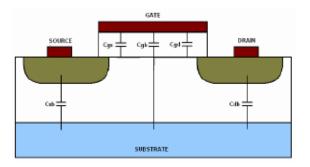

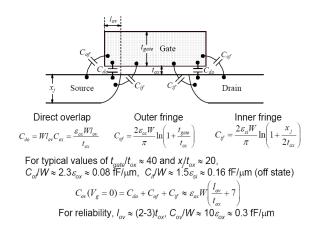

Based on physical structure of MOSFET, its parasitic capacitances can be classified into two major groups:- the gate capacitive effect (indicated by  $C_{0X}$ ) and- junction capacitances *drain-body* and *source-body*. These two capacitive effects can be modeled by including capacitances in the MOSFET model between its four terminals, G, D, S, and B as shown in Fig.2. There will be five capacitances:  $C_{gs}$ ,  $C_{gd}$ ,  $C_{gb}$ ,  $C_{sb}$  and  $C_{db}$  where the subscripts indicate the terminals shown in below figures 1,2,3,4,5.

Fig(2)

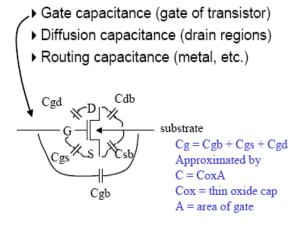

Three main forms:

Figure (3)

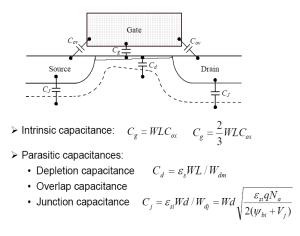

Figure (4)

International Journal of Scientific & Engineering Research Volume 3, Issue 12, December-2012 ISSN 2229-5518odd page

Figure(5)

## 3. Performance Analysis and Simulation Results:-

|                                                 | Reference   | Reference   |               |         |

|-------------------------------------------------|-------------|-------------|---------------|---------|

| parameter                                       | paper.12    | paper.13    | Proposed work | % saved |

|                                                 |             |             |               |         |

| Power (µw)                                      | 9.417       | 5.4         | 3.5           | 63      |

|                                                 |             |             |               |         |

| Area(µm <sup>2</sup> )                          | 306         | 504         | 92            | 71      |

| Leakage current(Ion+Ioff)A                      | 1.65mA+40nA | 1.65mA+40nA | 0.64mA+22nA   | 55      |

| Point A Total                                   | 6.39        | 15.06       | 1.82          | 72      |

| Capacitance(fF)                                 | 1.43        | 2.93        | 0.25          |         |

| Metal capacitance<br>Crosstalk capacitance      | 0.02        | 0.01        | 0.00          |         |

| Diffusion capacitance                           | 0.09        | 0.07        | 0.04          |         |

| Gate capacitance                                | 4.87        | 12.06       | 1.53          |         |

| Point B Total                                   |             |             |               |         |

| capacitance(fF)                                 | 7.79        | 17.94       | 2.89          | 63      |

| Metal capacitance                               | 2.84        | 5.91        | 1.12          |         |

| Cross talk capacitance<br>Diffusion capacitance | 0.08        | 0.04        | 0.00          |         |

| Gate capacitance                                | 0.24        | 0.20        | 0.08          |         |

| L. L        | 4.71        | 11.84       | 1.68          |         |

| Point C Total                                   |             |             |               |         |

| capacitance(fF)                                 | 7.50        | 10.07       | 1.99          | 74      |

3

International Journal of Scientific & Engineering Research Volume 3, Issue 12, December-2012 ISSN 2229-55180dd page

| Metal capacitance<br>Cross talk capacitance<br>Diffusion capacitance<br>Gate capacitance | 2.48<br>0.05<br>0.15<br>4.87 | 5.44<br>0.03<br>0.13<br>4.50 | 0.36<br>0.00<br>0.04<br>1.59 |    |

|------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|----|

| Carry Total capacitance (fF)                                                             | 2.92                         | 5.48                         | 0.41                         | 86 |

| Metal capacitance                                                                        | 2.08                         | 5.26                         | 0.33                         |    |

| Cross talk capacitance                                                                   | 0.02                         | 0.01                         | 0.00                         |    |

| Diffusion capacitance                                                                    | 0.24                         | 0.22                         | 0.08                         |    |

| Gate capacitance                                                                         | 0.00                         | 0.00                         | 0.00                         |    |

|                                                                                          |                              |                              |                              |    |

| Sum Total capacitance(fF)                                                                | 2.71                         | 4.87                         | 0.40                         | 86 |

| Metal capacitance                                                                        | 2.47                         | 4.46                         | 0.32                         |    |

| Cross talk capacitance                                                                   | 0.03                         | 0.02                         | 0.00                         |    |

| Diffusion capacitance                                                                    | 0.24                         | 0.20                         | 0.08                         |    |

| Gate capacitance                                                                         | 0.00                         | 0.00                         | 0.00                         |    |

|                                                                                          |                              |                              |                              |    |

| Delay                                                                                    | 0.47                         | 0.66ns                       | 0.22ns                       | 72 |

f means femoto  $(10^{-15})$

Table.1 . Comparison of results previous work and proposed work.

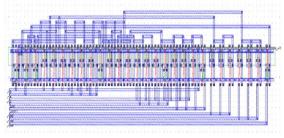

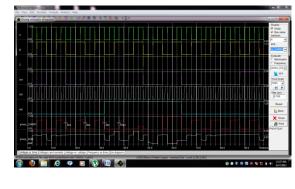

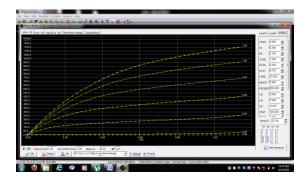

The results are compared with the previous work we shown that table.1 that Power is saved 63%, 55% of leakage current, 72% of total capacitance at input A, 63% of total capacitance at input C, 86% of total capacitance at sum, 86% of total capacitance at carry, 88% of gate capacitance,77% of diffusion capacitance,86% of metal capacitance ,100% of crosstalk capacitance ,72% of delay, and 71% of Area .Simulation results Shown in below figures (4-12) We have performed simulations using 90 Nanometer (nm) Micro wind 3 CMOS layout CAD Tool for design.

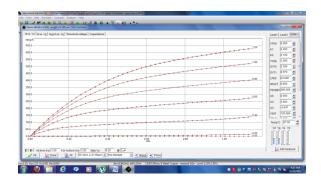

Fig (5) Reference .12 power report

Fig (4) Reference .12 layout design

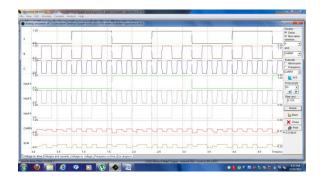

Fig (6) Reference .12 leakage current

Fig (7) Reference.13 layout design

Fig (8) Reference .13 power report

# Fig (9) Reference .12 leakage current

# Fig (10) Proposed work Layout optimization

Fig (11) Proposed work leakage current

Fig (12) Proposed work power report

# 4. Conclusion:-

The results are compared with the previous work and we shown that Power is saved 63%, 55% of leakage

current, 72% of total capacitance at input A, 63% of total capacitance at input B, 74% of total capacitance at input C, 86% of total capacitance at sum, , 86% of total capacitance at carry, 88% of gate capacitance,77% of diffusion capacitance ,86% of metal capacitance and 100% of crosstalk capacitance , 99% of delay, and 71% of Area. We have performed simulations using 90 Nanometer (nm) Micro wind 3 CMOS layout CAD Tool for design. Further power can be saved by using high and low threshold voltage and by using various parameters through Layout optimization.

#### 5. References:-

- [1] Jan M. Rabaey, Anantha Chandrakasan and Borivoje Nikolic, "Digital Integrated Circuits- A Design Perspective",2 nd ed., Prentice Hall of India Pvt Ltd, New Delhi,2006.

- [2]. S. Goel, M. A. Elgamel and M. A. Bayoumi, "DesignnMethodologies

Transl. on Circuits and Systems—I: Regular Papers, vol. 53, No. 4, April 2006.

[3]. P. M. Lee, C. H. Hsu and Y. H. Hung, "Novel 10-T full addersrealized by GDI structure", Proc. on Intl. Symp. on Integrated Circuits (ISIC2007), pp.115-118.

[4]. Suhwan Kim, Chang Jun Choi, Deog-Kyoon

[4]. Suhwan Kim, Chang Jun Choi, Deog-Kyoon Jeong, Stephen V.Kosonocky, Sung Bae Park," Reducing Ground-Bounce Noise and Stabilizing the Data-Retention Voltage of Power-Gating Structures,"*IEEEtransactionson Electron Devices*, Vol.55, No.1, January2008.

[5] Charbel J. Akl, Rafic A. Ayoubi, Magdy A. Bayoumi, "An effective staggered-phase damping technique for suppressing power-gating resonance noise during mode transition," 10th International Symposium on Quality of Electronic Design, pp.116-119, 2009.

- [6] K. Kawasaki et al., "A sub-us wake-up time power gating technique with bypass power line for rush current support," *IEEE J. Solid-State Circuits*, vol.44, no. 4, pp.146–147, Apr. 2009.

- [7]. Ku He, Rong Luo, Yu Wang, "A Power Gating Scheme for Ground Bounce Reduction During Mode Transition, " in ICCD07, pp. 388-394, 2007.

- [8] Deepa Sinha, Tripti Sharma, K.G.Sharma, Prof.B.P.Singh Design and analysis of low power 1 bit full adder cell IEEE paper 2011,978-1-4244 -8679-3/11/\$26.00 ©2011 IEEE

- [9] Mueller J, Caruyer G, Thoma R, Bernicot C, Juge A. Extrinisic, parasitic capacitance contributions of MOSFETs, their impact on performance, and their modeling. In: Proceedings of the 36th European solid-state device research conference; 2006. p. 323–6.

- [10]. Sudhama C, Spulber O, McAndrew C, Thoma R. Numerical simulation and analytical modeling of strong-inversion gate capaci- tance ultra-short in (30 nm) MOSFETs. In: Proceedings of the international conference on modeling and simulation of microsystems, Nanotech 2001, Nov 2001, p. 450-3.

- [11]. Suzuki K. Parasitic capacitance of submicrometer MOSFET's. IEEE Trans Electron Dev 1999;46:1895–900.

- [12] Dayadi.Lakshmaiah, Dr.M.V.Subramanyam, Dr.K.Satya Prasad, A Novel low power 1-Bit Full adder cell with the Gate Diffusion Input Based on MTCMOS & SSCMOS. IJAST march 2012 London,U.K

- [13].Dayadi.Lakshmaiah, Dr.M.V.Subramanyam, Dr.K.SatyaPrasad, Low power cmos 1-Bit Full adder cell. Based on voltage IOSR-JECE July 2012.Australiya

International Journal of Scientific & Engineering Research Volume 3, Issue 12, December-2012 ISSN 2229-55180dd page

Dayadi.Lakshmaiah is currently pursuing PhD Research scholar ECE Department, JNTUniversity, Kakinada, and working as Asso.professor Nizam Institute of Engineering and Technology Deshmuki Hyderabad .AndraPradesh (State), India. He Received B.Tech Degree in ECE From National Institute of Technology, Warangal (RECW) and M.Tech (DSCE) Degree From JNTUA Anantapur Andhra Pradesh He has published 8 International Journals..

Dr.M.V.Subramanyam Professor of ECE, currently working as Principal of Santhiram Engineering College Nandyal, Andhra Pradesh, India. He has 22 years of Experience in Teaching. He authored 4 text books, STLD, Computer Networks, Basic Electronics and Microprocessor& Microcontroller Interfacing and Application. He published more than 48 Technical papers in various National and International Journals and Conferences', He has an Editorial Member for the 4 International journal and 3 National Journals. "His Area of interest is Adhoc Wireless Networks, Cellular and Mobile Communications. He has Received B.Tech & M.Tech in ECE from JNTU, Hyderabad, PhD (Adhoc wireless Networks) Degree from JNTUH, Hyderabad, Andhra Pradesh, India. He has completed 5 research projects sponsored by the IE(I), India and currently one research project in hand which is funded by AICTE, New Delhi.

Dr. K. Sathaya Prasad Professor of ECE is currently working as Rector of JNTUK, Kakinada. He has more than 32 years of experience in teaching and 25 years of R & D. He is an expert in Digital Signal Processing. He has Guided to 10Ph.D's and guiding 10Ph.D scholars. He authored Electronic Devices and Circuits text book. He held different positions in his career like Head of the Department, vice principal, and principal for JNTU Engineering College (JNTUK). He published more than 60 technical papers in National and International Journals and conferences. He also received best Teacher Award from Govt of Andhra Pradesh in 2010. He is Received B.Tech Degree in ECE from JNTUA Anantapur, M.E (Communication Systems) Degree from University of Madras, and Ph.D (signal Processing) Degree from the Indian Institute of Technology Madras, India.